# Федеральное государственное бюджетное учреждение науки Институт проблем проектирования в микроэлектронике Российской академии наук (ИППМ РАН)

## Библиотека схемотехнических решений

Входной дифференциальный каскад быстродействующего операционного усилителя на комплементарных полевых транзисторах для работы при низких температурах

Пахомов И.В., <u>ilyavpakhomov@gmail.com</u>, Бугакова А.В., <u>annabugakova.1992@mail.ru</u>,

Титов А.Е., <u>alex.evgeny.titov@gmail.com</u>, Жук А.А., <u>alexey.zhuk96@mail.ru</u> Научно-исследовательская лаборатория проблем проектирования в экстремальной микроэлектронике ИППМ РАН и Донского государственного технического университета (г. Ростов-на-Дону)

### 1. Области применения

Предлагаемый дифференциальный каскад (ДК) на комплементарных полевых транзисторах с управляющим p-n переходом (СЈГЕТ) предназначен для применения в качестве IP модуля в аналоговых и аналого-цифровых микросхемах систем связи, автоматики и приборостроения в условиях низких температур. При этом радиационная стойкость и низкотемпературный диапазон обеспечиваются за счет применения СЈГЕТ [1].

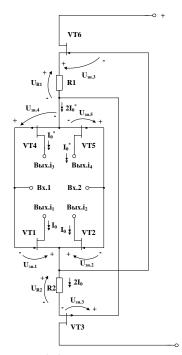

Рис. 1 Схема входного СЈГЕТ дифференциального каскада на комплементарных полевых транзисторах.

Для работы при низких температурах при жестких ограничениях на уровень шумов перспективно использование JFet полевых транзисторов с управляющим рп переходом [1-3]. ДК данного класса активно применяются в структуре малошумящих аналоговых интерфейсов для обработки сигналов датчиков [4-6]. Электрическая схема предлагаемого ДК, представлена на рис. 1.

Практическая реализация схемы рис. 1 может быть осуществлена (при определенной доработке) в рамках других технологий, например, по CBiCJFET комплементарному биполярному техпроцессу (АО «НПП Пульсар», г. Москва) и др.

#### 2. Описание схемы

Входной дифференциальный каскад (рис.1) включает:

- потенциальные входы (Bx.1, Bx.2) и токовые выходы ( $Bыx._{i1}$ - $Bыx._{i4}$ ) устройства,

- входные полевые транзисторы (VT1-VT2, VT4-VT5),

- вспомогательные полевые транзисторы (VT3, VT6),

- резисторы (R1, R2).

Существенная особенность ДК рис. 1 состоит в том, что в нем идентичный статический режим по токам входных полевых транзисторов VT1-VT2 и VT4-VT5 устанавливается не отдельными источниками опорного тока, а интегрированной в единый функциональный узел цепью стабилизации статического режима ДК, включающей как единое целое входные полевые транзисторы, а также дополнительные полевые транзисторы с управляющим p-n переходом VT3 и VT6. Следует заметить, что статический режим ДК практически не зависит от величины входного синфазного сигнала  $u_c = u_{c1} = u_{c2}$  и изменений напряжений на шинах источников питания. Это позволяет исключить из схемы ДК рис. 1 традиционные источники опорного тока, отрицательно влияющие на его многие параметры (особенно при их простейшем построении). При этом независимо от численных значений напряжения отсечки применяемых полевых транзисторов с р и п-каналами ток общей истоковой цепи входных полевых транзисторов VT1-VT2 (ток через резистор R2) всегда равен току общей истоковой цепи входных полевых транзисторов VT4-VT5 (току через резистор R1). Это важное свойство предлагаемой схемы ДК способствует ее симметрии.

Если на Bx.1 подается положительное входное напряжение  $u_{Bx}$  относительно Bx.2, то это вызывает увеличение тока входных полевых транзисторов VT1 и VT5 и уменьшение тока истока входных полевых транзисторов VT2 и VT4.

Предлагаемая схема ДК имеет повышенные значения коэффициента ослабления входных синфазных сигналов и коэффициента подавления помех по шинам питания. Этот эффект обусловлен тем, что для типовых ДК данные параметры определяются двумя основными факторами [7, 8]:

- конечной величиной выходных сопротивлений источников опорного тока в классических схемах;

- неидентичностью коэффициентов внутренней обратной связи применяемых полевых транзисторов.

Первый фактор в предлагаемом ДК отсутствует, т.к. источники опорного тока здесь не нужны, а статический режим схемы устанавливается элементами, «изолированными» от шин источников питания. В конечном итоге предлагаемый ДК (при таких же активных элементах, как и в классических схемах) имеет улучшенные значения коэффициента ослабления входных синфазных сигналов и коэффициента подавления помех по шинам питания.

образом, предлагаемый IΡ модуль имеет существенные преимущества в сравнении с известными схемотехническими решениями ДК класса dual-input-stage [9-35], что позволяет рекомендовать его для практического различных ОУ И построения низкотемпературных использования В радиационно-стойких аналоговых микросхем по JFET техпроцессам OAO «Интеграл» (г. Минск), а также CBiCJFET комплементарному биполярнополевому технологическому процессу АО «НПП «Пульсар» (г. Москва).

#### 3. Компьютерное моделирование входного дифференциального каскада

В частном случае схема ДК рис. 1 исследовалась в среде LTSpice IV на моделях библиотеки CJFet транзисторов Дворникова О.В. (МНИПИ, г. Минск).

Рис. 2 Графическое изображение полевых транзисторов с каналом n-типа (a) и p-типа (б) в среде LTSpice.

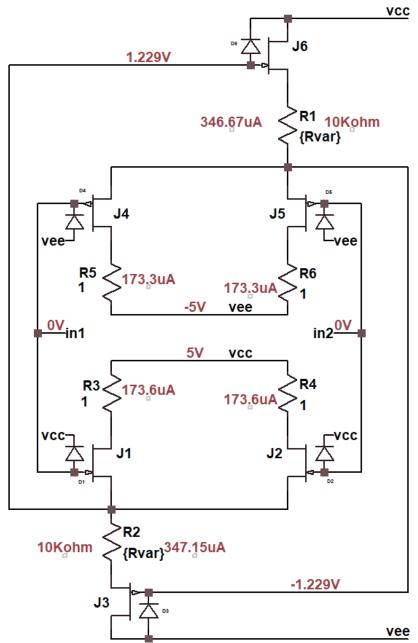

На рис. 3 показана схема ДК в среде LTspice.

Рис. 3 Схема ДК (рис. 1) в среде LTspice на моделях CJFet транзисторов.

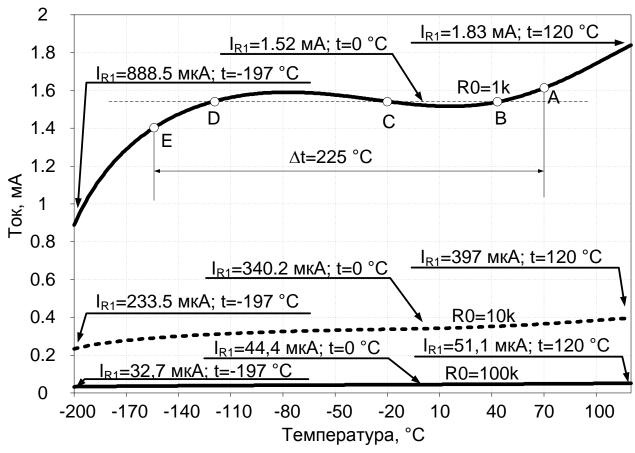

Графики, представленные на рис. 4, снятые при разных температурах и численных значениях сопротивлений R1=R0, R2=R0, подтверждают сделанные выше качественные выводы относительно стабильности статического режима. Действительно, зависимость токов через резисторы R1=R2=R0=1 кОм (рис. 4) имеет участок АЕ, в пределах которого статические токи общей истоковой цепи ДК изменяются незначительно. Это позволяет обеспечить за счет рационального выбора параметров элементов улучшенную стабильность статического режима ДК.

Рис. 4 Зависимость тока общей истоковой цепи ДК рис.3, протекающего через резистор R1=R2=R0 от температуры

Результаты компьютерного моделирования в среде LTspice схемы ДК рис. 3 показывают, что на основе предлагаемого ДК реализуется широкий спектр температурных зависимостей выходных токов ДК. В итоге, это позволяет проектировать дифференциальные и мультидифференциальные операционные усилители с заданными параметрами статического режима в диапазоне температур.

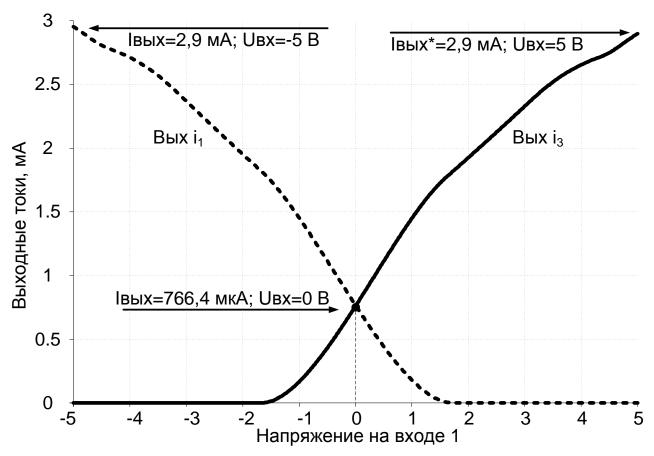

Особенность предлагаемого ДК состоит в том, что он фактически работает в режиме класса AB (рис. 5). Действительно, при нулевом входном сигнале выходные статические токи ДК в 3,8 раза меньше, чем выходные токи при большом входном сигнале. Это позволяет получить в ОУ на основе предлагаемого ДК более высокие (в 3,8 раза) значения максимальной скорости нарастания выходного напряжения [7,8].

Рис. 5 Зависимость выходных токов ДК от входного дифференциального напряжения при t=27C и R1=R15=1 кОм, R2=R16=1 кОм.

#### 4. Параметры оптимизации

Параметрами оптимизации ДК рис. 1 являются: относительная нестабильность статического тока общей истоковой цепи ДК в заданном температурном диапазоне при ограничениях на изменение проводимости передачи ДК, статическое токопотребление, геометрические параметры полевых транзисторов, уровень радиации, быстродействие и т.п.

# 5. Netlist в LTSpice схемы рис.3

```

* D:\simulation\LTSpice\Scheme_205\\\Pi8681.asc J5 vcc N001 N002 JN260_2 \\

D2 N001 vcc DJN260_2 {JNV} \\

J1 N004 in1 N003 JP50_2 \\

D5 vee in1 DJP50_2 {JPV} \\

J2 N005 0 N003 JP50_2 \\

D8 vee 0 DJP50_2 {JPV} \\

J6 vee N003 N008 JP50_2 \\

D6 vee N003 DJP50_2 {JPV} \\

R2 N001 N008 10k \\

R1 N002 N003 10k

```

```

J3 N006 in1 N001 JN260 2

D9 in1 vcc DJN260 2 {JNV}

J4 N007 0 N001 JN260 2

D10 0 vcc DJN260 2 {JNV}

R5 vcc N006 1

R6 vcc N007 1

R3 N004 vee 1

R4 N005 vee 1

V4 vcc 0 5 Rser=0.00001

V5 0 vee 5

V1 in1 0 {VS}

.model D D

.lib C:\Users\Elija\OneDrive\Documents\LTspiceXVII\lib\cmp\standard.dio

.model NJF NJF

.model PJF PJF

.lib C:\Users\Elija\OneDrive\Documents\LTspiceXVII\lib\cmp\standard.jft

.param LT=-197

.temp={LT}

* .ac dec 100 1 100Meg

* .tran 0 1m 0 1u

* .step param LT -197 27 2

* .step param Dg 1 1Meg 300

* .step dec param fn 1e12 1e18 1e2

.param fn=1

.param Dg=1

.param VS=0

.lib C:\LT\CJFET 3.lib

.param weight=250

.param JNV={weight/260}

.param JPV={weight/50}

.param I1=1u

.step param VS -5 5 0.1

* .step param R1 10k 20k 30k

.param fit=1

* .step param V1 0 5 10m

* .param R1=100k

* .param R2=100k

.backanno

.end

```

При этом использовались компьютерные модели JFET транзисторов, разработанных Дворниковым Олегом Владимировичем (г. Минск, МНИПИ, oleg\_dvornikov@tut.by).

Исследование выполнено за счет гранта Российского научного фонда (проект № 16-19-00122-П).

## Список литературы

1. K. O. Petrosyants, M. R. Ismail-zade, L. M. Sambursky, O. V. Dvornikov, B. G. Lvov and I. A. Kharitonov, "Automation of parameter extraction procedure for Si JFET SPICE model in the -200...+110°C temperature range," 2018 Moscow Workshop on Electronic and Networking Technologies (MWENT), Moscow, 2018, pp. 1-5. DOI: 10.1109/MWENT.2018.8337212

- 2. Создание низкотемпературных аналоговых ИС для обработки импульсных сигналов датчиков. Часть 2 / О. Дворников, В. Чеховский, В. Дятлов, Н. Прокопенко // Современная электроника, 2015, № 5. С. 24-28

- 3. O. V. Dvornikov, N. N. Prokopenko, N. V. Butyrlagin and I. V. Pakhomov, "The differential and differential difference operational amplifiers of sensor systems based on bipolar-field technological process AGAMC," 2016 International Siberian Conference on Control and Communications (SIBCON), Moscow, 2016, pp. 1-6. DOI: 10.1109/SIBCON.2016.7491792

- 4. Дворников О.В., Чеховский В.А., Дятлов В.Л., Прокопенко Н.Н. "Малошумящий электронный модуль обработки сигналов лавинных фотодиодов" Приборы и методы измерений, по. 2 (7), 2013, pp. 42-46.

- 5. Дворников О. Чеховский В., Дятлов В., Прокопенко Н. Применение структурных кристаллов для создания интерфейсов датчиков //Современная электроника. 2014. N2. 1. С. 32-37.

- 6. O. V. Dvornikov, A. V. Bugakova, N. N. Prokopenko, V. L. Dziatlau and I. V. Pakhomov, "The microcircuits MH2XA010-02/03 for signal processing of optoelectronic sensors," 2017 18th International Conference of Young Specialists on Micro/Nanotechnologies and Electron Devices (EDM), Erlagol, 2017, pp. 396-402. DOI: 10.1109/EDM.2017.7981781

- 7. Прокопенко Н.Н. Нелинейная активная коррекция в прецизионных аналоговых микросхемах (монография) // Ростов-на-Дону: Изд-во Северо-Кавказского научного центра высшей школы, 2000. 222с.

- 8. Операционные усилители с непосредственной связью каскадов: монография / Анисимов В.И., Капитонов М.В., Прокопенко Н.Н., Соколов Ю.М. Л.: «Энергия», 1979. 148 с.

- 9. Патент US 5.291.149 fig. 4, 1994 г.

- 10.Патент US 4.377.789, fig. 1, 1983 г.

- $11.\Pi$ атентная заявка US 2006/0125522, 2006 г.

- 12.Патент US 7.907.011, 2011

- 13.US 2008/0024217, fig. 1, 2008  $\Gamma$ .

- 14.Патент ЕР 0318263,1989 г.

- 15.Патент US 5.907.259, fig. 1, 1999 г.

- 16.Патент US 7.408.410, 2008 г.

- 17. Патент US 6.628.168, fig.2, 2003 г.

- 18.Патентная заявка US 2009/0302895, 2009 г.

- 19.Патент US 5.714.906, fig. 4, 1998 г.

- 20.Патент US 2005/0285677, 2005 г.

- 21.Патент US 5.070.306, fig. 3, 1991 г.

- 22.Патент US 2010/001797, 2010 г.

- 23.Патент US 6.972.623, fig. 4, fig. 6, 2005 г.

- 24.Патент US 2008/0252374, 2008 г.

- 25.Патент US 7.586.373, 2009 г.

- 26.Патент US 2006/0215787, 2006 г.

- 27.Патент US 7.453.319, 2008 г.

- 28.Патент US 2004/0174216, fig. 2, 2004 г.

- 29.Патент US 7.215.200, fig. 6, 2007 г.

- 30.Патент US № 6.433.637, fig. 2, 2002 г.

- 31.Патент US № 6.392.485, 2002 г.

- 32.Патент US 5.963.085, fig. 3, 1999 г.

- 33.Патент US 6.788.143, 2004 г.

- 34.Патент US 4.390.850, 1983 г.

- 35.Патент US 6.696.894, fig. 1, 2004 г.