# Федеральное государственное бюджетное учреждение науки Институт проблем проектирования в микроэлектронике Российской академии наук (ИППМ РАН)

# Библиотека схемотехнических решений

Двоичный токовый пороговый RS-триггер

Бутырлагин Н.В., nbutyrlagin@mail.ru, Прокопенко Н.Н., prokopenko@sssu.ru, Югай В.Я., yugtag@gmail.com, Пахомов И.В., pahom2191@mail.ru Игнашин А.А., igan 96@mail.ru

Научно-исследовательская лаборатория проблем проектирования в экстремальной микроэлектронике ИППМ РАН и Донского государственного технического университета (г. Ростов-на-Дону)

#### 1. Области применения двоичного токового порогового RS-триггера

Построение компонентов цифровых управляющих и вычислительных систем, например, роботов и беспилотных летательных аппаратов, базируется на использовании RS-триггеров [1]. Применение линейной алгебры в качестве математического аппарата логического синтеза цифровых структур [2] позволяет получить логическую, а на ее основе – схемотехническую, реализацию линейных аналогов указанных логических функций [3]. Эти схемотехнические решения могут быть затем использованы для построения специализированных токовых логических IP-модулей и цифровых СФ-блоков на их основе.

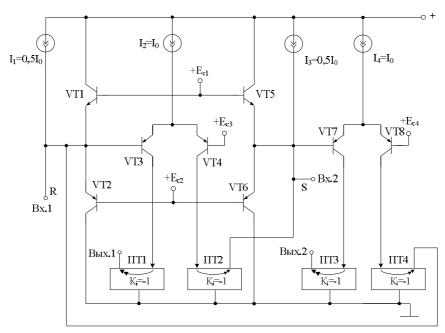

Рис. 1 Схема ВіЈТ двоичного токового порогового RS-триггера

Практическая реализация схемы рис. 1 может быть осуществлена при определенной доработке в рамках других различных технологий: TSMC (BiCMOS), SiGe (IHP, Германия), HHGRACE SoI (кремний на изоляторе), H10-CMOS090\_LP (AO «Микрон», г. Зеленоград), 3КБТ (ВіЈFеt-биполярно-полевой техпроцесс, АО «Интеграл», г. Минск), комплементарный биполярный техпроцесс (АО «НПП Пульсар», г. Москва) и др.

#### 2. Описание схемы двоичного токового порогового RS-триггера

Схема двоичного токового порогового RS-триггера рис.1 [4] включает:

- логические входы Bx.1 и Bx.2 (R и S),

- выходы устройства (Вых.1 и Вых.2),

- входные транзисторы (VT1-VT2, VT5-VT6),

- дифференциальные каскады (VT3-VT4, VT7-VT8),

- источники напряжения смещения (E<sub>c1</sub>-E<sub>c4</sub>),

- источники опорного тока  $(I_1-I_4)$ ,

- токовые зеркала (ПТ1-ПТ4).

Рассмотрим работу двоичного токового порогового RS-триггера (рис. 1).

Для схемотехнической реализации логических элементов используются токовые зеркала и дифференциальные каскады (ДК), реализующие пороговые функции. Для двоичных переменных логический ноль представляется отсутствием некоторого заданного кванта тока  $I_0$ , а единица - наличием кванта тока Іо. При этом знак кванта определяется его направлением (втекающим, вытекающим). При токовом сигнальном представлении логических переменных направление тока не влияет на значение переменной, а зависит только от знака слагаемых в операциях алгебраического суммирования, реализующих выражения линейной алгебры [2-3]. Объединение таких логических элементов в более сложные структуры требует согласования не только уровней квантов тока  $I_0$ , но и направлений входных и выходных токовых логических сигналов.

Традиционные сигналы установки заявляемого триггера в единичное (R) или нулевое (S) состояния поступают в виде квантов вытекающего тока на логические входы устройства. Режим хранения -R=S=0, для установки в одно из состояний подаётся сигнал (R) на соответствующий вход, R=S=1 — запрещенная комбинация (Таблица 1).

Таблица 1 – Таблица истинности порогового RS-триггера с прямыми входами

| R | S | <b>y</b> 1 | $y_2$    | Примечание             |

|---|---|------------|----------|------------------------|

| 0 | 0 | Хранение   | Хранение | хранение предыдущее    |

|   |   |            |          | состояния              |

| 0 | 1 | 1          | 0        | -                      |

| 1 | 0 | 0          | 1        | -                      |

| 1 | 1 | X          | X        | запрещенная комбинация |

Входная переменная «R» в виде кванта втекающего тока поступает на логический вход (R) устройства и далее на объединённые эмиттеры входных транзисторов VT1-VT2, а также на базу транзистора VT3, где из него вычитается 0,5 кванта вытекающего тока источника опорного тока I<sub>1</sub>. Режимы работы входных транзисторов задаются значениями напряжений источников напряжения смещения  $E_{c1}$ - $E_{c2}$  и обеспечивают предотвращение насыщения транзисторов источника опорного тока I<sub>2</sub>. Транзисторы VT3-VT4 образуют дифференциальный каскад (ДК). Переключение коллекторных токов этих транзисторов определяется сигналом, поступающим на базу транзистора VT3. ДК в данном случае выполняет функции порогового элемента, выполняя сравнение переменной «R» с пороговым уровнем 0,5. Выбор такого порогового уровня обеспечивает независимость результатов преобразования сигналов от погрешностей преобразования пределах 0,5 кванта тока І<sub>0</sub>. Разностный сигнал, поступая на эмиттеры входных транзисторов VT1-VT2 формирует соответствующее знаку этой разности входное напряжение ДК на базе транзистора VT3. Сигнал с коллектора транзистора VT3 в виде сигнала вытекающего тока подается на токовое зеркало ПТ1, где преобразуется в равный ему сигнал втекающего тока и подается на выход устройства Вых.1. Сигнал с коллектора транзистора VT4 в виде сигнала вытекающего тока подается на токовое зеркало ПТ2, где преобразуется в равный ему сигнал втекающего тока и подается на объединённые эмиттеры входных транзисторов VT5-VT6, а также на базу транзистора VT7, где из него вычитается 0,5 кванта вытекающего тока источника опорного тока І1. Входная переменная «S» в виде кванта втекающего тока поступает на логический вход устройства (S) и далее на объединённые эмиттеры входных транзисторов VT5-VT6. Транзисторы VT7-VT8 дифференциальный образуют каскад (ДК). Переключение коллекторных токов этих транзисторов определяется сигналом, поступающим на базу транзистора VT7. ДК в данном случае выполняет функции порогового элемента, выполняя сравнение переменной «S» с пороговым уровнем 0,5. Выбор обеспечивает порогового уровня независимость результатов такого преобразования сигналов от погрешностей преобразования в пределах 0,5 кванта тока I<sub>0</sub>. Разностный сигнал, поступая на эмиттеры входных транзисторов VT5-VT6 формирует соответствующее знаку этой разности входное напряжение ДК на базе транзистора VT7. Сигнал с коллектора транзистора VT7 в виде сигнала вытекающего тока подается токовое зеркало ПТЗ, где преобразуется в равный ему сигнал втекающего тока и подается на Вых.2. Сигнал с коллектора транзистора в виде сигнала вытекающего тока подается на токовое зеркало ПТ4, где преобразуется в равный ему сигнал втекающего тока и подается на Вх.1, образуя 100% положительную обратную связь. Переключение ДК, выполняющих функции пороговых элементов, и, следовательно, переключение триггера в новое состояние происходит в моменты, когда соответствующий входной сигнал «R» для ДК на транзисторах VT3-VT4 или «S» для ДК на транзисторах VT7-VT8 принимает значение 1 ( $I_0$ ).

## 3. Компьютерное моделирование двоичного токового порогового RSтриггера

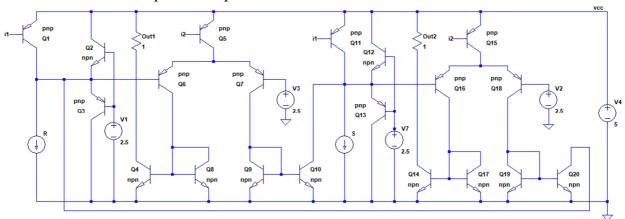

В частном случае схема двоичного токового порогового RS-триггера рис. 1 исследовалась в среде LTspice на моделях транзисторов AБМК\_2.2.1 (АО «Интеграл», г. Минск [5-6]).

Рис. 2 Графическое изображение n-p-n и p-n-p транзисторов АБМК 2.2.1

# 3.1 Двоичный токовый пороговый RS-триггер с прямым включением входов

На рис. 3 показана схема двоичного токового порогового RS-триггера с прямыми входами в среде LTspice.

Рис. 3 Схема рис. 1 с прямыми входами в среде LTspice на моделях транзисторов AБМК 2.2.1

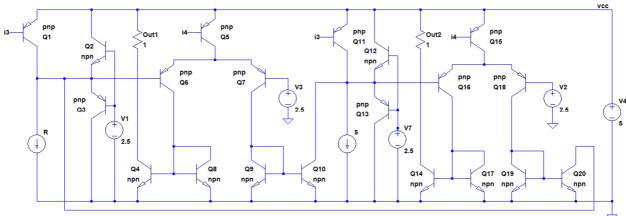

На рис. 4 показана схема двоичного токового порогового RS-триггера с инверсными входами в среде LTspice.

Рис. 4 Схема рис. 1 с инверсными входами в среде LTspice на моделях транзисторов AБМК 2.2.1

#### 4. Ожидаемые параметры двоичного токового порогового RS-триггера

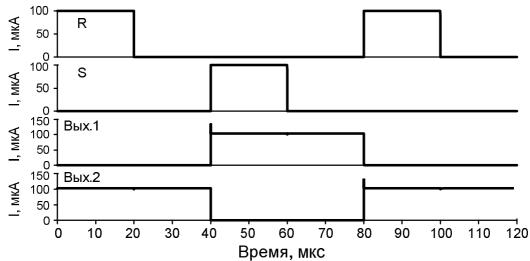

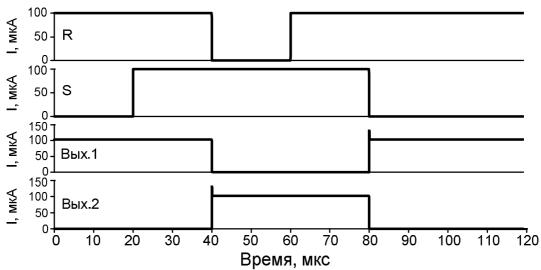

На рис.5 приведены осциллограммы входных и выходных сигналов схемы двоичного токового порогового RS-триггера (рис. 3) с прямым включением входов.

Рис. 5. Осциллограммы входных и выходных сигналов схемы двоичного токового порогового RS-триггера с прямыми входами

На рис.6 приведены осциллограммы входных и выходных сигналов схемы двоичного токового порогового RS-триггера (рис. 4) с инверсным включением входов.

Рис. 6. Осциллограммы входных и выходных сигналов схемы двоичного токового порогового RS-триггера с инверсными входами

#### 4. Параметры оптимизации

Оптимизации подлежат: значения токов дополнительных источников опорного тока  $I_1-I_4$ , а также значения напряжений источников напряжения смещения ( $E_{c1}$ - $E_{c4}$ ) для корректирования режимов работы транзисторов входного и дифференциального каскадов.

### 5. Netlist в Spice (рис.3)

- 1: D:\simulation\LTSpice\Scheme 197\8125.asc

- 2: V4 vcc 0 5

- 3: Q1 N013 i1 vcc 0 pnp

- 4: Q11 N015 i1 vcc 0 pnp

- 5: Q5 N011 i2 vcc 0 pnp

- 6: Q10 N015 N018 0 0 npn

- 7: Q9 N018 N018 0 0 npn

- 8: Q2 vcc N009 N013 0 npn

- 9: Q3 0 N009 N013 0 pnp

- 10: V1 N009 0 2.5

- 11: V2 N016 0 2.5

- 12: Q7 N018 N014 N011 0 pnp

- 13: Q6 N017 N013 N011 0 pnp

- 14: Q4 N021 N017 0 0 npn

- 15: Q8 N017 N017 0 0 npn

- 16: Q12 vcc N010 N015 0 npn

- 17: Q13 0 N010 N015 0 pnp

- 18: V3 N014 0 2.5

- 19: Q21 i1 i1 N001 0 pnp

- 20: Q22 N005 i1 N001 0 pnp

- 21: I1 i1 0 50µ

- 22: R2 N005 0 1

- 23: V8 N001 0 5

- 24: Q18 N020 N016 N012 0 pnp

- 25: Q16 N019 N015 N012 0 pnp

- 26: Q15 N012 i2 vcc 0 pnp

- 27: Q17 N019 N019 0 0 npn

- 28: Q14 N022 N019 0 0 npn

- 29: Q20 N013 N020 0 0 npn

- 30: Q19 N020 N020 0 0 npn

- 31: R§Out1 vcc N021 1

- 32: R§Out2 vcc N022 1

- 33: V7 N010 0 2.5

- 34: Q23 i2 i2 N002 0 pnp

- 35: Q24 N006 i2 N002 0 pnp

- 36: I2 i2 0 100µ

- 37: R1 N006 0 1

- 38: V5 N002 0 5

- 39: Q25 i3 i3 N003 0 pnp

- 40: Q26 N007 i3 N003 0 pnp

- 41: I3 i3 0 50  $\mu$

- 42: R3 N007 0 1

- 43: V6 N003 0 5

- 44: Q27 i4 i4 N004 0 pnp

- 45: Q28 N008 i4 N004 0 pnp

- 46: I7 i4 0 100µ

- 47: R4 N008 0 1

- 48: V9 N004 0 5

- 49: I§S N015 0 PWL(0 0 40u 0 40.005u 100u 60u 100u 60.005u 0 110 0)

- 50: I§R N013 0 PWL(0 100u 20u 100u 20.005u 0 80u 0 80.005u 100u 100u 100u 100.005u 0 110 0)

- 51: I§RR 0 0 PWL(0 100u 40u 100u 40.005u 0 60u 0 60.005u 100u 100 100u)

- 52: I§SS 0 0 PWL(0 0 20u 0 20.005u 100u 80u 100u 80.005u 0 100u 0)

- 53: .model NPN NPN

- 54: .model PNP PNP

- 55: .lib C:\Users\Elija\OneDrive\Documents\LTspiceXVII\lib\cmp\standard.bjt

- 56: .op

- 57: .param LT=25

- 58: .temp= $\{LT\}$

- 59: .ac dec 100 1 100Meg

- 60: .tran 0 1m 0 1u

- 61: .step param LT -197 27 2

- 62: .step param Dg 1 1Meg 300

- 63: .step dec param fn 1e12 1e18 1e2

- 64: .param fn=1

- 65: .param Dg=1

- 66: .param V1=1.8

- 67: .lib C:\LT\ABMK-2.2-1.lib

- 68: .param weight=250

- 69: .param JNV={weight/260}

- 70: .param JPV={weight/50}

- 71: .param I1=1u

- 72: .step param V1 -5 5 50m

- 73: .step param I1 1u 1m 10u

- 74: .param fit=1

- 75: .tran 0 120u 0 0.1u

- 76: .backanno

- 77: .end

# Netlist в Spice (рис.4)

- 1: D:\simulation\LTSpice\Scheme 197\8125.asc

- 2: V4 vcc 0 5

- 3: Q1 N013 i1 vcc 0 pnp

- 4: Q11 N015 i1 vcc 0 pnp

- 5: Q5 N011 i2 vcc 0 pnp

- 6: Q10 N015 N018 0 0 npn

- 7: Q9 N018 N018 0 0 npn

- 8: Q2 vcc N009 N013 0 npn

- 9: Q3 0 N009 N013 0 pnp

- 10: V1 N009 0 2.5

- 11: V2 N016 0 2.5

- 12: Q7 N018 N014 N011 0 pnp

- 13: Q6 N017 N013 N011 0 pnp

- 14: Q4 N021 N017 0 0 npn

- 15: Q8 N017 N017 0 0 npn

- 16: Q12 vcc N010 N015 0 npn

- 17: Q13 0 N010 N015 0 pnp

- 18: V3 N014 0 2.5

- 19: Q21 i1 i1 N001 0 pnp

- 20: Q22 N005 i1 N001 0 pnp

- 21: I1 i1 0 50µ

- 22: R2 N005 0 1

- 23: V8 N001 0 5

- 24: Q18 N020 N016 N012 0 pnp

- 25: Q16 N019 N015 N012 0 pnp

- 26: Q15 N012 i2 vcc 0 pnp

- 27: Q17 N019 N019 0 0 npn

- 28: Q14 N022 N019 0 0 npn

- 29: Q20 N013 N020 0 0 npn

- 30: Q19 N020 N020 0 0 npn

- 31: R§Out1 vcc N021 1

- 32: R§Out2 vcc N022 1

- 33: V7 N010 0 2.5

- 34: Q23 i2 i2 N002 0 pnp

- 35: Q24 N006 i2 N002 0 pnp

- 36: I2 i2 0 100μ

- 37: R1 N006 0 1

- 38: V5 N002 0 5

- 39: Q25 i3 i3 N003 0 pnp

- 40: Q26 N007 i3 N003 0 pnp

- 41: I3 i3 0 150µ

- 42: R3 N007 0 1

- 43: V6 N003 0 5

- 44: Q27 i4 i4 N004 0 pnp

- 45: Q28 N008 i4 N004 0 pnp

- 46: I7 i4 0 100μ

- 47: R4 N008 0 1

- 48: V9 N004 0 5

- 49: I§S N015 0 PWL(0 0 40u 0 40.005u 100u 60u 100u 60.005u 0 110 0)

- 50: I§R N013 0 PWL(0 100u 20u 100u 20.005u 0 80u 0 80.005u 100u 100u 100u 100.005u 0 110 0)

- 51: I§RR 0 0 PWL(0 100u 40u 100u 40.005u 0 60u 0 60.005u 100u 100 100u)

- 52: I§SS 0 0 PWL(0 0 20u 0 20.005u 100u 80u 100u 80.005u 0 100u 0)

- 53: .model NPN NPN

- 54: .model PNP PNP

- 55: .lib C:\Users\Elija\OneDrive\Documents\LTspiceXVII\lib\cmp\standard.bjt

- 56: .op

- 57: .param LT=25

- 58: .temp= $\{LT\}$

- 59: .ac dec 100 1 100Meg

- 60: .tran 0 1m 0 1u

- 61: .step param LT -197 27 2

- 62: .step param Dg 1 1Meg 300

- 63: .step dec param fn 1e12 1e18 1e2

- 64: .param fn=1

- 65: .param Dg=1

- 66: .param V1=1.8

- 67: .lib C:\LT\ABMK-2.2-1.lib

- 68: .param weight=250

- 69: .param JNV={weight/260}

- 70: .param JPV={weight/50}

- 71: .param I1=1u

- 72: .step param V1 -5 5 50m

- 73: .step param I1 1u 1m 10u

- 74: .param fit=1

- 75: .tran 0 120u 0 0.1u

- 76: .backanno

- 77: .end

Исследование выполнено при финансовой поддержке РФФИ в рамках научного проекта № 18-37-00061.

При этом использовались компьютерные модели транзисторов, разработанных Дворниковым Олегом Владимировичем (г.Минск, МНИПИ, oleg dvornikov@tut.by).

# Список литературы

- 1. Поспелов Д. А. Логические методы анализа и синтеза схем. Изд. 3-е, перераб. и доп., М., «Энергия», 1974, 368 с.

- 2. Prokopenko N.N., Chernov N.I., Yugai V.Ya. Basic Concept of Linear Synthesis of Multi-Valued Digital Structures in Linear Spaces. Proceeding of IEEE East-West Design & Test Symposium (EWDTS'2013). Rostov-on-Don, Russia, September 27-30, 2013. pp. 146-149. DOI: 10.1109/EWDTS.2014.7027045

- 3. Prokopenko N.N., Chernov N.I., Yugai V.Ya. Schematic Design of Digital IC at the Base of Linear Algebra. ICSES 2014 International Conference on Signals and Electronic Systems, September 11-13, 2014, Poznan, POLAND. DOI: 10.1109/ICSES.2014.6948728.

- 4. Двоичный токовый пороговый RS-триггер: заявка на патент РФ; МПК:  $H03K\ 3/037$ ,  $H03K\ 19/00$  / Н.В. Бутырлагин, Н.И. Чернов, Н.Н. Прокопенко, В.Я. Югай № 2018145482; Заявл. 21.12.2018

- 5. K.O. Petrosyants, M. Ismail-zade, O.V. Dvornikov et al. "Automation of parameter extraction procedure for Si JFET SPICE model in the—200...+ 110° C temperature range", Moscow Workshop on Electronic and Networking Technologies, pp. 1-6, 2018.

- 6. O. V. Dvornikov, V. L. Dziatlau, N. N. Prokopenko, K. O. Petrosiants, N. V. Kozhukhov and V. A. Tchekhovski, "The accounting of the simultaneous exposure of the low temperatures and the penetrating radiation at the circuit simulation of the BiJFET analog interfaces of the sensors," 2017 International Siberian Conference on Control and Communications (SIBCON), Astana, Kazakhstan, 2017, pp. 1-6. DOI: 10.1109/SIBCON.2017.7998507