# Федеральное государственное бюджетное учреждение науки Институт проблем проектирования в микроэлектронике Российской академии наук (ИППМ РАН)

## Библиотека схемотехнических решений

Быстродействующий операционный усилитель на основе «перегнутого» каскода: модификация ОУ- SR №7

Прокопенко H.H., <u>prokopenko@sssu.ru</u>, Бугакова А.В., <u>annabugakova.1992@mail.ru</u>, Бутырлагин H.B., <u>nbutyrlagin@mail.ru</u>

Научно-исследовательская лаборатория проблем проектирования в экстремальной микроэлектронике ИППМ РАН и Донского государственного технического университета (г. Ростов-на-Дону)

#### 1. Области применения ОУ- SR №7

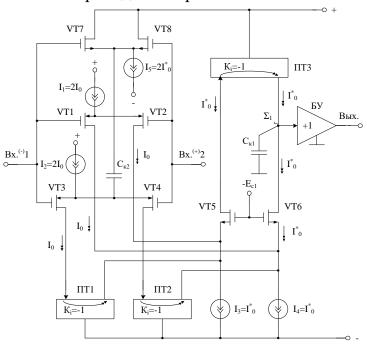

Предназначен для работы в аналоговых и аналого-цифровых устройствах автоматики и приборостроения, в том числе в системах на кристалле (СнК). Схема КМОП варианта ОУ приведена на рис. 1.

Рис. 1. Быстродействующий КМОП ОУ на основе «перегнутого» каскода

Практическая реализация архитектуры рис. 1 может быть осуществлена как на КМОП, так и на BiJT транзисторах: tsmc (BiCMOS), SiGe (IHP, Германия), HHGRACE SoI (кремний на изоляторе), HCMS8D, H10-CMOS090\_LP (АО «Микрон», г. Зеленоград), 3КБТ (ВiJFet-биполярно-полевой техпроцесс, АО «Интеграл», г. Минск), комплементарный биполярный техпроцесс АО «НПП Пульсар», г. Москва и др.

## 2. Текстовое описание схемы КМОП ОУ рис. 1

Схема ОУ рис.1 включает:

- базовый входной каскад VT1-VT4,

- корректирующий каскад VT7-VT8,

- промежуточный каскад на основе токовых зеркал ПТ1, ПТ2, ПТ3[1] и «перегнутого» каскода (VT5-VT6),

- источники тока  $I_1$ ,  $I_2$ , устанавливающие статический режим входного каскада VT1-VT4,

- источники тока  $I_3$ ,  $I_4$ , устанавливающие статический режим «перегнутого» каскода VT5-VT6,

- источник тока I<sub>5</sub>, устанавливающий статический режим корректирующего каскада VT7-VT8,

- буферный усилитель (БУ),

- интегрирующую цепь коррекции Ск1,

- дифференцирующую цепь коррекции Ск2.

Интегрирующая емкость коррекции  $C_{\kappa 1}$  обеспечивает заданный запас устойчивости ОУ по фазе. Дифференцирующий конденсатор  $C_{\kappa 2}$  повышают быстродействие ОУ в режиме большого сигнала при работе входных транзисторов в режиме микротоков и практически не влияют на малосигнальную частоту единичного усиления ОУ  $(f_1)$ .

В КМОП ОУ рис. 1 источники тока  $I_1$ ,  $I_2$  - устанавливают статический режим входных транзисторов VT1-VT4, источники тока  $I_3$ ,  $I_4$  - определяют статический режим выходных транзисторов VT5-VT6, источник тока  $I_5$  - задает статический режим транзисторов VT7-VT8. Все эти токи могут изменяться в широких пределах (единицы микроампер — единицы миллиампер). Это существенно влияет на максимальную скорость нарастания выходного напряжения ОУ (SR), которая достигает наибольших значений в сильноточном режиме VT1-VT4. При миллиамперных токах (1-5 мА) КМОП VT1-VT4 эффективность применения цепи коррекции  $C_{\kappa 2}$  уменьшается [2].

Разомкнутый коэффициент усиления по напряжению ОУ рис. 1 определяется эквивалентным сопротивлением в высокоимпедансном узле  $\Sigma 1$  и существенно зависит от выходного сопротивления токового зеркала ПТЗ. В качестве токового зеркала ПТЗ могут применяться более 50 известных схемотехнических решений [1], что обеспечивает получение численных значений Ку в широком диапазоне (до 80 дБ). Рациональный выбор токовых зеркал — один из важных этапов проектирования и оптимизации схемы ОУ рис.1.

В режиме большого сигнала токовые зеркала ПТ1, ПТ2 исключают ограничение выходного тока «перегнутого» каскода, перезаряжающего ёмкость  $C_{\kappa 1}$ .

В качестве буферного усилителя (БУ) могут применяться более 30 вариантов классических схем, отличающихся друг от друга энергетическими и динамическими параметрами.

Таким образом, схема рис. 1 — это некоторая обобщенная схема ОУ, в рамках которой для основных технологических процессов (ВЈТ, КМОП) можно реализовать десятки частных вариантов ОУ, отличающихся друг от друга схемотехникой БУ, токовых зеркал ПТ1-ПТ3 [1], и, как следствие, динамическими параметрами.

В этой связи компьютерное моделирование обобщенной функциональной схемы рис. 1 с идеальными токовыми зеркалами, БУ и источниками тока  $I_1$ ,  $I_2$ ,  $I_3$ ,  $I_4$ ,  $I_5$  позволяет определить предельные параметры широкого класса практических вариантов построения ОУ [3] с архитектурой рис. 1, к которым необходимо стремиться.

### 3. Компьютерное моделирование ОУ рис. 1

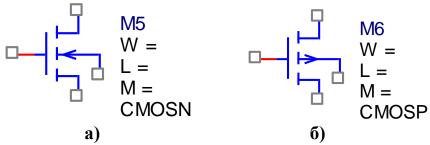

В частном случае схема ОУ рис. 1 исследовалась в среде Orcad 9.2 на моделях КМОП транзисторов tsmc\_035\_t65.

Рис. 2 Графическое изображение КМОП транзисторов tsmc\_035\_t65 с n- и рканалами

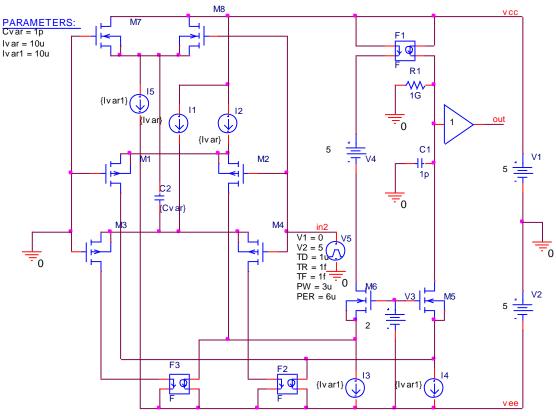

На рис. 3 показана схема КМОП ОУ рис.1 в среде Orcad.

Рис. 3 КМОП ОУ рис. 1 в среде Orcad 9.2 на моделях транзисторов tsmc\_035\_t65

## 4. Ожидаемые параметры и характеристики ОУ рис. 3

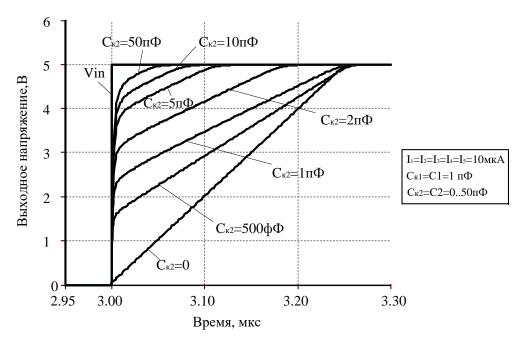

Компьютерное моделирование влияния дифференцирующей емкости коррекции  $C2=C_{\kappa 2}$  на переходные процессы в КМОП ОУ рис. 3 при  $C_{\kappa 1}=C1=1\pi\Phi$ ,  $C_{\kappa 2}=C2=0..50\pi\Phi$ , Ri=1 ГОм, и работе его входного (DIS) и промежуточного каскадов в микрорежиме ( $I_1=I_2=I_3=I_4=I_5=10$ мкА), иллюстрируют графики рис. 4.

Рис. 4 Переходные процессы КМОП ОУ рис. 3: передний фронт

Зависимость максимальной скорости нарастания выходного напряжения ОУ рис.3 (SR) от ёмкости дифференцирующего конденсатора ( $C_{\kappa 2}$ = $C_{\nu ar}$ ) при  $I_1$ = $I_2$ = $I_3$ = $I_4$ = $I_5$ =10мкA, Ri=1 ГОм,  $C_{\kappa 1}$ = $C_1$ =1 $\pi$ Ф, полученные из графиков рис. 4, представлены в табл. 1.

Табл. 1 Зависимость SR от ёмкости дифференцирующих конденсаторов  $C_{\kappa 2} = C2 = 0 \div 50 \pi \Phi$

| Ёмкость коррекции           | Передний фронт            | Задний фронт              |

|-----------------------------|---------------------------|---------------------------|

| $C_{\kappa 2}$ =C2=Cvar, пФ | SR <sup>(+)</sup> , В/мкс | SR <sup>(-)</sup> , В/мкс |

| 0                           | 19,7                      | 19,67                     |

| 0,5                         | 18,34                     | 19,23                     |

| 1                           | 20,20                     | 21,97                     |

| 2                           | 30,07                     | 36,19                     |

| 5                           | 65,25                     | 141,84                    |

| 10                          | 135,59                    | 540,54                    |

| 50                          | 366,97                    | 909,09                    |

Моделирование показало, что быстродействие рассматриваемого КМОП ОУ при отсутствии дифференцирующей цепи коррекции ( $C_{\kappa 2}$ =0) пропорционально статическим токам  $I_1$ = $I_2$ . В то же время в микрорежиме VT1-VT4 скорость нарастания SR при  $C_{\kappa 2}$ =0 существенно уменьшается. Главная причина этого эффекта — уменьшение на один-два порядка напряжения ограничения ( $U_{rp}$ ) проходной характеристики драйвера емкости коррекции  $C_{\kappa 1}$  [2] (транзисторы VT1-VT4, токовые зеркала ПТ1-ПТ3, «перегнутый» каскод VT5-VT6), которое оказывает доминирующее влияние на SR  $\approx 2\pi f_1 U_{rp}$ , где  $f_1$  — малосигнальная частота единичного усиления скорректированного ОУ,  $U_{rp}$  — напряжение ограничения проходной характеристики драйвера емкости коррекции  $C_{\kappa 1}$  [3].

Анализ табл. 1 и рис. 4 показывает, что  $C_{\kappa 2}$  может существенно повысить быстродействие ОУ рис.1 (до 45 раз). При этом переходный процесс (рис. 4) имеет два явно выраженных участка — «крутой» и «пологий». Если максимальную скорость нарастания ОУ рассчитывать по формуле, которая усредняет численные значения SR с двумя участками переходного процесса [3], то положительный эффект от применения  $C_{\kappa 2}$  может быть найден из уравнения  $SR \approx 0.9 U_{out}/t_{yet}$ , где  $t_{yet}$  — время установления переходного процесса на уровне  $0.9 U_{out}$ ,  $U_{out}$  — установившееся значение выходного напряжения.

Если SR рассчитывать как максимальную производную выходного напряжения ОУ (не обращая внимания на "пологий" участок переходного процесса) [3], то численные значения SR с  $C_{\kappa 2}$  будут существенно выше.

Таким образом, компьютерное моделирование показывает, что при статических токах КМОП входных транзисторов на уровне 10 мкА применение дифференцирующей цепи коррекции ( $C_{\kappa 2}$ ) обеспечивает увеличение SR ОУ рис.1 в 45 раз.

При этом, дифференцирующая цепь коррекции  $(C_{\kappa 2})$  оказываются неэффективной в сильноточных режимах входного каскада, т.к. в этом случае

диапазон его активной работы составляет единицы вольт [2]. Этого достаточно для получения высоких значений SR и без применения  $C_{\kappa 2}$ .

Компьютерное моделирование схемы ОУ рис. 3 при  $I_1=I_2=2$ мкА,  $I_3=I_4=I_5=10$ мкА,  $R_1=I_5=I_0$  показывает, что предельный разомкнутый коэффициент усиления (Ку) равен 56 дБ, а верхняя граничная частота (по уровню -3дБ) – 341 кГц. В конкретных схемах данные параметры существенно зависят от свойств токового зеркала ПТЗ [1].

### 5. Параметры оптимизации схемы рис.1

Практический интерес представляет определение оптимальных значений  $C_{\kappa 1}$ ,  $C_{\kappa 2}$  и статических токов входного и промежуточного каскадов  $I_1$ ,  $I_2$ ,  $I_3$ ,  $I_4$ ,  $I_5$  при заданных ограничениях на максимальную скорость нарастания выходного напряжения ОУ, разомкнутый коэффициент усиления, запас устойчивости по фазе, энергопотребление, ослабление синфазных сигналов, геометрию транзисторов, схемотехнику токовых зеркал (более 50 модификаций [1]) и буферного усилителя (более 30 модификаций) и т.п.

## 6. Netlist в Spice OУ (рис.3)

```

1: source OP_AMP

2: X_F1 VCC N40498 VCC N01683 SCHEMATIC1_F1

3: I I2

VCC N38914 DC {Ivar}

4: E GAIN1

OUT 0 VALUE {1 * V(N01683)}

5: I I4

N41052 VEE DC {Ivar1}

6: X F2

N49530 VEE N41052 VEE SCHEMATIC1 F2

7: I I3

N39827 VEE DC {Ivar1}

8: M M4

N49530 IN2 N00905 N00905 CMOSP

9: + L=0.35u

10: + W = 10u

11: + M=1

12: C_C1

0 N01683 1p

13: V_V1

VCC 0 5

14: M_M5

N01683 N41313 N41052 N41052 CMOSN

15: + L=0.35u

16: + W = 10u

17: + M=1

18: V V2

0 VEE 5

19: C_C2

N00905 N60424 {Cvar}

VCC 0 N60424 N60424 CMOSN

20: M_M7

21: + L=0.35u

22: + W = 10u

```

```

23: + M=1

24: M M2

N39827 IN2 N38914 N38914 CMOSP

25: + L=0.35u

26: + W = 10u

27: + M=1

28: X_F3 N13638 VEE N39827 VEE SCHEMATIC1_F3

N51584 N41313 N39827 N39827 CMOSN

29: M M6

30: + L=0.35u

31: + W=10u

32: + M=1

33: I I5

N60424 VEE DC {Ivar1}

34: V_V3

N41313 VEE 2

35: R_R1

0 N01683 1G

36: M_M1

N41052 0 N38914 N38914 CMOSP

37: + L=0.35u

38: + W = 10u

39: + M=1

40: M M8

VCC IN2 N60424 N60424 CMOSN

41: + L=0.35u

42: + W = 10u

43: + M=1

44: V_V4

N40498 N51584 5

45: V V5

IN2 0 AC 1

46: +PULSE 0 5 1u 1f 1f 3u 6u

47: I I1

VCC N00905 DC {Ivar}

N13638 0 N00905 N00905 CMOSP

48: M M3

49: + L=0.35u

50: + W = 10u

51: + M=1

52: .PARAM Cvar=1p Ivar1=1u Ivar=1u

53: .subckt SCHEMATIC1_F1 1 2 3 4

54: F_F1

3 4 VF_F1 1

55: VF F1

1 2 0V

56: .ends SCHEMATIC1 F1

57: .subckt SCHEMATIC1 F2 1 2 3 4

58: F_F2

3 4 VF_F2 1

59: VF F2

1 2 0V

60: .ends SCHEMATIC1_F2

61: .subckt SCHEMATIC1_F3 1 2 3 4

62: F_F3

3 4 VF_F3 1

63: VF F3

1 2 0V

64: .ends SCHEMATIC1_F3

```

Разработка выполнена в рамках гранта Российского научного фонда (проект № 16-19-00122)

## Список литературы:

- 1. Прокопенко Н.Н., Титов А.Е., Бутырлагин Н.В. Токовые зеркала для проектирования КМОП аналоговых микросхем: основные модификации (ТЗ №1-№ 36) [Электронный ресурс] // Институт проблем проектирования в микроэлектронике РАН: [сайт]. [2018]. URL: http://www.ippm.ru/data/eljrnal/paper/J4.pdf (дата обращения: 17.04.2018)

- 2. Prokopenko N.N., Butyrlagin N.V., Bugakova A.V., The Comparative Analysis of the Maximum Slew Rate of the Output Voltage BJT and CMOS (SiGe TSMC 0.35μ) Operational Amplifiers, 19th International Conference of Young Specialists on Micro/Nanotechnologies and Electron Devices (EDM2018), June 29 July 3 2018, Erlagol, Altai Republic, Russia, pp. 712-717.

- 3. Прокопенко, Н.Н. Архитектура и схемотехника быстродействующих операционных усилителей: монография / Н.Н. Прокопенко, А.С. Будяков. Шахты: Изд-во ЮРГУЭС, 2006. 231 с. ISBN 5-93834-261-9