## Система синхронизации с повышенной помехоустойчивостью

${\it HO.\Phi.}$  Адамов<sup>1,2</sup>,  ${\it E.C.}$  Балака<sup>2</sup>,  ${\it A.C.}$  Михмель<sup>2</sup>

## Synchronization system with high noise immunity

Yu.F. Adamov<sup>1,2</sup>, E.S. Balaka<sup>2</sup>, A.S. Mikhmel<sup>2</sup>

<sup>1</sup> National Research University of Electronic Technology, Moscow

Аннотация. С повышением степени интеграции микросхем повышается и уровень перекрестных помех. Одновременно, возрастают требования к их помехоустойчивости. Повышение амплитуды импульсных сигналов — простой и эффективный метод повышения помехоустойчивости. В статье обсуждается система синхронизации с глобальным распределением низковольтного синхросигнала и локальным повышением амплитуды с использованием драйверов с повышением напряжения. Предложенные технические решения позволяют установить амплитуду синхросигнала индивидуально для каждого функционального блока.

*Ключевые слова:* синхронизация, помехоустойчивость, драйверы синхросигнала, повышение амплитуды, сокращение числа источников и шин электропитания.

Abstract. The crosstalk level increases with increasing degree of circuit integration. At the same time, requirements to their noise immunity increase. The increase in the amplitude of the pulse signals is a simple and effective method to improve noise immunity. The article discusses the synchronization system with the global distribution of low-voltage clock signal and a local increase in the amplitude using drivers with increasing voltage. Proposed technical solutions allow to set the amplitude of the clock signal individually for each functional unit.

*Keywords:* synchronization, noise immunity, clock signal drivers, amplitude increase, source and power rail reduction

Введение. Развитие технологий направлено на увеличение степени интеграции, быстродействия и энергоэффективности. При этом снижается напряжение питания, устойчивость схемы к перегрузкам и помехам. В цифровых микросхемах система синхронизации имеет наибольшую длину проводников и распределена на всей площади кристалла. Соответственно, максимальная вероятность сбоя схемы определяется сбоеустойчивостью системы синхронизации. На сбоеустойчивость влияет логический перепад синхросигнала. Для повышения амплитуды управляющего сигнала необходимо введение в схему дополнительной шины электропитания или дополнительного каскада

<sup>&</sup>lt;sup>1</sup> Национальный исследовательский университет «МИЭТ»

<sup>&</sup>lt;sup>2</sup> Институт проблем проектирования в микроэлектронике РАН

<sup>&</sup>lt;sup>2</sup> Institute for Design Problems in Microelectronics RAS

импульсного повышения амплитуды сигнала. В настоящей работе предложена схема драйвера синхросигнала с повышенной амплитудой управления выходными КМОП транзисторами.

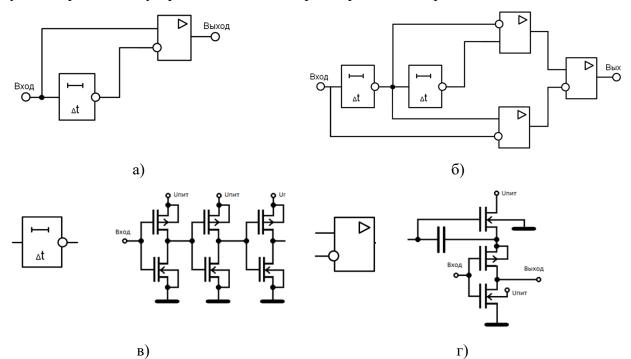

**Драйверы синхросигнала**. Драйвер импульсов с повышенной амплитудой включает два параллельных каскада (рис. 1a), управляемых входным сигналом с амплитудой равной напряжению питания.

Выходной импульс с повышенной амплитудой формируется срезом входного сигнала. Выходное напряжение повышается до уровня напряжения питания. Разделительный конденсатор  $C_p$  заряжается до напряжения равного ( $u_{num}$  -  $u_{nop}$ ), где  $u_{num}$  - напряжение источника питания,  $u_{nop}$  - пороговое напряжение NMOП транзистора. Напряжение на выходе линии задержки повышается, когда NMOП транзистор в драйвере уже закрыт, РМОП открыт, а выходное напряжение достигло максимального уровня с учетом порогового напряжения NMOП транзистора. Напряжение на выходе продолжит повышение до уровня ( $2 \cdot u_{num}$  -  $u_{nop}$ ).

Снижение напряжения питания микросхем, и повышение порогового напряжения МОП транзисторов с целью энергосбережения снижают эффективность импульсного повышения напряжения. Для дальнейшего повышения амплитуды управляющих импульсов предложено устройство, схема которого приведена на рис. 16.

Рис. 1. Формирователь импульсов с повышенной амплитудой

а) простая электрическая схема формирователя; б) двухэтапный преобразователь напряжения; в) инвертирующая линия задержки;

г) инвертирующий драйвер с дополнительным NMOП транзистором в цепи питания.

Повышение амплитуды импульсов осуществляется в два этапа. Для этого в устройстве используются две последовательно включенные линии задержки и три повышающих драйвера. На первом этапе две линии задержки и два драйвера формируют два сигнала с повышенной амплитудой, отличающиеся сдвигом во времени, соответствующим линии задержки. На втором этапе сигналы с повышенной амплитудой подаются на входы третьего повышающего драйвера. При этом амплитуда импульса выходного сигнала возрастает до величины  $(3 \cdot u_{num} - 2 \cdot u_{nop})$ .

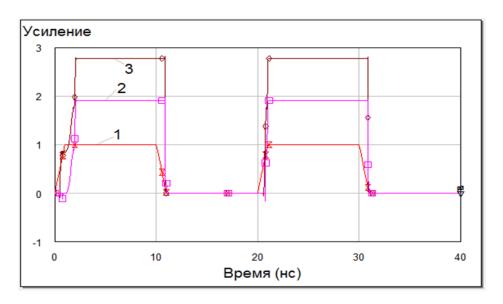

На рис. 2 показаны результаты моделирования формы управляющих сигналов в режиме с нагрузкой в виде КМОП инвертора с суммарной шириной транзисторов 2 мм.

- 1 входной сигнал; 2 выходной сигнал после первого этапа преобразования;

- 3 выходной сигнал после второго этапа преобразования

*Puc.2*. Результаты моделирования двухэтапного преобразователя при напряжении питания 1В

Исключение дополнительного источника питания и уменьшение размеров выходных транзисторов оценено авторами как уменьшение активной площади кристалла на  $0.5 \div 1$  мм $^2$ , и соответствующее упрощение конструктивных решений при применении изделий.

Заключение. Применение драйверов, повышающих амплитуду синхросигнала позволяет установить оптимальный уровень синхросигнала для каждого функционального блока. При этом не требуются дополнительные источники и шины питания. Снижается общее число драйверов, используемых для распределения информации на кристалле микросхемы.

## Литература

- 1. Документация на микросхемы фирмы SANYO LA 7837, LA 7838 [Электронный ресурс]. Режим доступа: http://master-tv.com (дата обращения: 01.11.2016).

- 2. Пат. 120297 Российская Федерация, ПМ. Источник высокого знакопеременного напряжения, программируемого по его амплитуде и частоте.

- 3. *Круглов Ю.В.* Интеграторы на переключаемых конденсаторах для широкополосных сигма-дельта модуляторов с большим динамическим диапазоном [Электронный ресурс]: дис. на соиск. учен. степ. к.т.н. / Круглов Ю.В.; МИЭТ. Москва, 2005. Режим доступа: http://tekhnosfera.com (дата обращения: 01.11.2016).

- 4. *Dessouky M., Kaiser A.* Very Low-Voltage Digital-Audio AS Modylator with 88 dB Dynamic Range Using Local Switch Bootstrapping // IEEE J. Solid-State Circuit. 2001. -- Vol. 36(3). -- pp. 349-355.

- 5. *Ong A., Prodanov V., Tarsia M.* A metod for reducing the variation in «ON» resistance of a MOS sampling switch // IEEE International Symposium on Circuits and systems. Geneva, 2000. May 28-31. –- pp. 437-440.

- Белоус В., Дрозд С., Листопадов А. Схемотехнические методы повышения помехоустойчивости цифровых КМОП микросхем // Компоненты и технологии. – 2010. -- №6.

- 7. *Адамов Ю.Ф.*, *Балака Е.С.*, *Рухлов В.С.* Схемотехника электронных устройств, работающих в условиях электромагнитных помех // Материалы конференции (МЭС-2016). -- Москва, 2016.

**Адамов Юрий Федорович** – доктор технических наук, профессор МИЭТ, в.н.с. ИППМ РАН. *Область научных интересов:* микроэлектроника, твердотельная электроника, технология микроэлектронных устройств. **E-mail: adamov@ippm.ru.**

**Екатерина Вячеславовна Балака** – кандидат технических наук, с.н.с. ИППМ РАН. Область научных интересов: микроэлектроника, схемотехника, надежность.

**Михмель Артем Сергеевич** — инженер-проектировщик 1-ой категории ИППМ РАН. Область научных интересов: микроэлектроника.